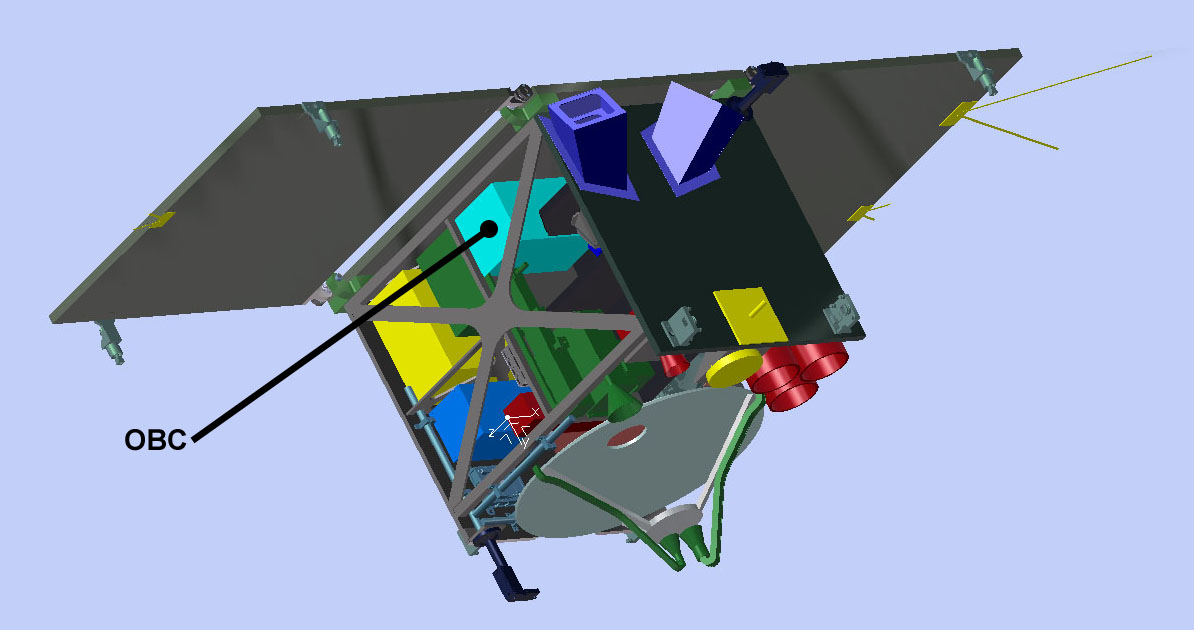

Projekt „Flying Laptop CPU“ (FLP CPU):

Neue Wege in der Satellitensteuerung…

Der erste Kleinsatellit der Universität Stuttgart wird mit einer neuen Art von Bordrechner ausgestattet. Ein System aus FPGA Modulen übernimmt die Steuerungsfunktionen eines herkömmlichen Satelliten Buscontrollers (SBC) und alle Aufgaben der Nutzlast-Datenverarbeitung.

Der Rechner wird vom TZR in Zusammenarbeit mit dem Fraunhofer Institut für Rechnerarchitektur und Softwaretechnik (FIRST) entwickelt.

Die Verwendung von FPGA Technologie ermöglicht:

- Hohe Geschwindigkeit der Datenverarbeitung

- Zeitlich präzise Ansteuerung von Systemkomponenten (insbesondere Lageregelung)

- Große Flexibilität

In der Satellitentechnik elementare Systemvoraussetzungen wie

- Niedriger Stromverbrauch

- Geringe Freisetzung von Wärme

- Kompakte Größe

- Strahlungstoleranz des Systems

können mit FPGA Technologie erreicht werden.

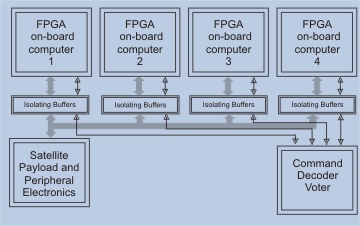

Aufbau des On-Board Computers:

Der On-Board Computer besteht aus vier identischen FPGA-Knoten. Diese sind an ein weiteres FPGA Modul, den Command-Decoder/Voter, angeschlossen, der aufgrund von Kontrollsummen aus den Knoten entscheidet, welcher der Computer die Kontrolle des Satelliten übernimmt. Sollte der Master nicht mehr korrekt laufen, zum Beispiel nach einem SEU (single event upset), wird sofort auf einen der anderen Knoten umgeschaltet, und der defekte Knoten kann neu gestartet werden. Durch die Verwendung der vierfachen Redundanz können für die Knoten kostengünstigere COTS (commercial off the shelf) Komponenten eingesetzt werden. Der Voter allein ist ein strahlungsfestes Bauteil für Raumfahrtanwendungen.

FPGA Programmierung

Die Programmierung des Bordrechners wird mit Hilfe von Handel-C realisiert. Handel-C ist eine Programmiersprache, die auf C basiert, allerdings auf die FPGA Programmierung zugeschnitten ist und die Implementierung paralleler Strukturen ermöglicht. Aus dem Programmcode wird eine Hardwareschaltung generiert und in das FPGA geschrieben. FPGAs können sehr oft umprogrammiert werden, was ihnen eine hohe Flexibilität verleiht.