“Flying Laptop CPU” (FLP CPU) Project:

Breaking new ground in satellite control…

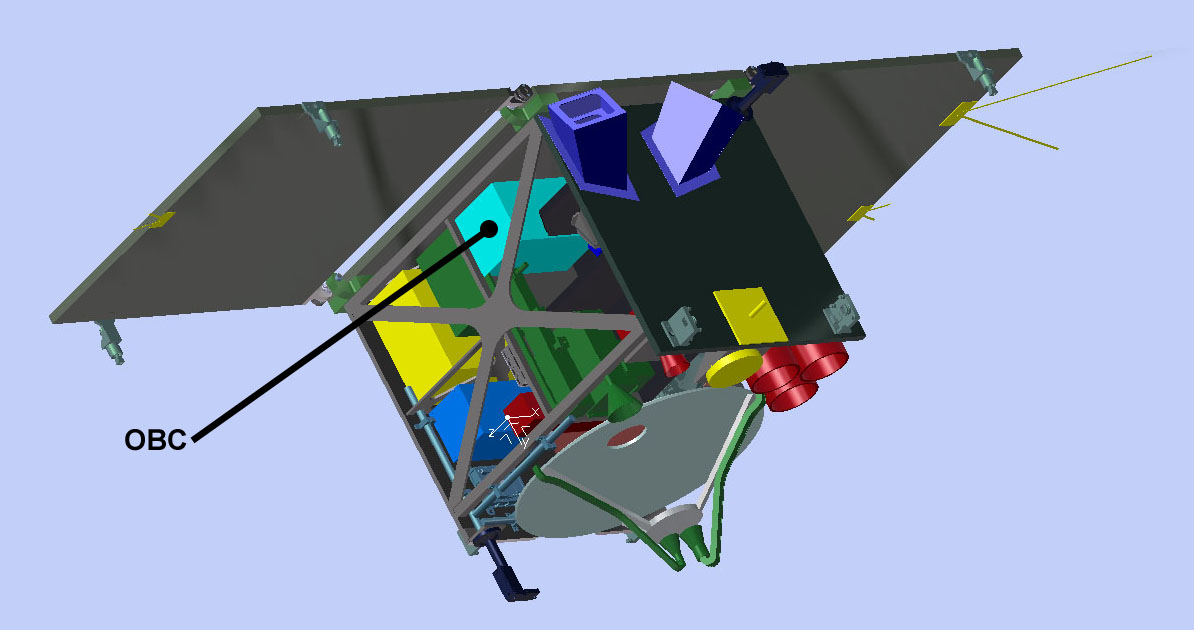

The first micro satellite designed by the Universit�t Stuttgart is equipped with a new kind of on-board computer. A system of FPGA modules handles the control functions of a conventional satellite bus controller (SBC) as well as the payload data processing.

The computer is developed by the TZR in cooperation with the Fraunhofer Institute Computer Architecture and Software Technology (FIRST).

The Utilization of FPGA Technology Offers:

- High speed data processing

- Precisely timed control of system devices (particularly attitude control)

- High flexibility

Primary objectives for satellite technology like

- Low power consumption

- Low heat dissipation

- Compact size

- Radiation tolerance of the system

can be addressed with FPGA technology.

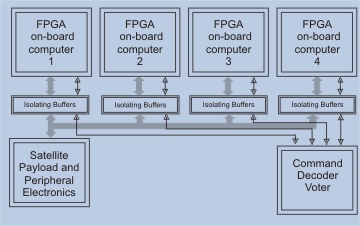

On-board Computer Design

The on-board computer consists of four identical FPGA nodes. They are connected to another FPGA module, the command-decoder/voter. On the basis of checksums that are transmitted regularly by the nodes the voter decides which of them takes over the control of the satellite. Should it detect a malfunction in the master node, e.g. caused by a single event upset (SEU), it instantly switches to a different node. The defective node can be restarted. Because of quadruple redundancy it is possible to use inexpensive commercial off the shelf (COTS) components for the nodes. Only the voter is a radiation hard component for space applications.

FPGA Programming

The programming of the on-board computer is realized with Handel-C. Handel-C is a programming language based on ANSI C adapted to FPGA programming that makes the implementation of parallel structures possible. The code is translated into a hardware netlist and written to the FPGA. FPGAs can be flexibly reprogrammed many times.